ADC(아날로그 디지털 변환회로)는 오늘날의 SoC 설계에서 흔히 볼 수 있습니다. 차세대 자동차, 모바일 및 고성능 컴퓨팅 애플리케이션은 더 적은 전력 소모량으로 더 많은 기능과 더 높은 성능을 제공하기 위해 나노미터 노드를 사용해야 합니다. ADC 사양을 충족하고 높은 수율의 설계를 만들기 위해 설계자들은 방대한 브루트 포스(Brute force) 혼성 신호 시뮬레이션을 수행하여 모든 잠재적 설계 편차를 고려해야 합니다. 하지만 나노미터 노드에서는 프로세스, 전압, 온도(PVT) 코너와 파라미터 편차가 기하급수적으로 증가하므로 시뮬레이션이 비실용적이고 많은 비용이 들게 됩니다. 따라서 설계 팀은 검증 사이클을 단축하기 위해 외삽법을 채택 해야 한다는 압력을 받고 있습니다.

Analog Value의 설계 팀은 설계 수율에 영향을 미칠 위험을 감수하고, 출시 시간 요구를 충족하기 위해 시간 영역 2단계 ADC를 검증하는 데 외삽법을 사용했습니다. 본 백서와 웨비나에서는 Analog Value사의 실제 사례 를 통해 기존의 통계 편차 검증 방법론을 사용할 때 어떠한 어려움에 직면했는지 그리고 어떻게 Solido™ Variation Designer™ 및 Symphony 통합 솔루션을 사용하여 강력한 편차 인식 혼성 신호 검증을 달성하고 설계 수율 요구 사항을 충족했는지 를 설명합니다.

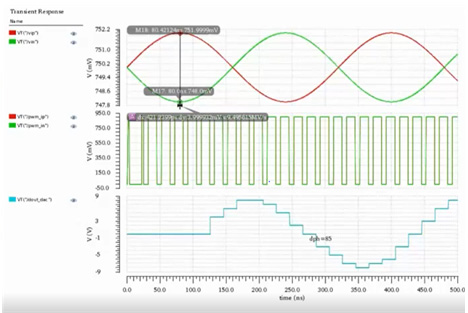

Analog Value 팀은 22nm FDSOI GlobalFoundries 노드를 사용하는 클라이언트의 자동차 RADAR 애플리케이션에 대해 시간 영역 2단계 ADC 아키텍처를 선택했습니다. 나노미터 프로세스 노드에 있는 기존의 전압 영역 고분해능 ADC는 공급 전압 레벨이 떨어질 때 동적 범위가 충분하지 않습니다. 반면에 시간 영역 2단계 ADC는 나노미터 노드에서 높은 분해능과 더 뛰어난 성능을 발휘합니다. 아날로그 입력을 시간 펄스로 변환한 후에 디지털 코드로 디지털화하기 때문입니다.

첨단 공정 노드에서 통계적 편차가 ADC의 성능에 미치는 영향을 기존의 검증 방법론을 이용해 알아내고 측정하기가 갈수록 어려워지고 있습니다. 디자이너는 ADC의 아날로그 하위 블록에 대해 광범위한 SPICE 시뮬레이션을 실행함으로써 가능한 모든 설계 편차를 확인해야 합니다. 그 다음에는 최상위 수준의 혼성신호 시뮬레이션을 실행해 통계적 편차가 ADC의 전반적인 성능(유효 비트 수 ENOB로 측정되는)에 미치는 영향을 알아내고 확인해야 합니다.

(주)채널5코리아 | 서울 금천구 디지털로 178 가산퍼블릭 A동 1824호 | 사업자등록번호 : 113-86-36448 | 대표자 : 명세환

청소년보호책임자 : 장은성 | 발행인, 편집인 : 명세환 | 전화 : 02-866-9957

등록번호 : 서울특별시 아 01366 | 등록일 : 2010년 10월 40일 | 제보메일 : news@e4ds.com

본 콘텐츠의 저작권은 e4ds뉴스 또는 제공처에 있으며 이를 무단 이용하는 경우 저작권법 등에 따라 법적책임을 질 수 있습니다.

Copyright © 2026 e4ds News. All Rights Reserved