JESD204B 인터페이스를 지원하는 아나로그 디바이스 클럭 솔루션

ADI / 권익승 기술이사

무명2016-07-19 오전 10:55:14

오늘 강의해 주신 기술을 통신 품질 분야에 적용 할수 있는지 궁금 합니다~ADI12016.07.19

HMC7044의 경우 상대적으로 우수한 phase noise 특성을 가지므로, 통신품질향상에 기여할 것으로 예상합니다.김*기2016-07-19 오전 10:53:55

동작온도의 범위가 궁금하군여..그리고, 온도에 따른 보정블럭이 존재하는지도 궁금하구여ADI12016.07.19

동작온도 범위는 -40C ~ +85C입니다. 온도에 따른 보정기능은 없습니다.무명2016-07-19 오전 10:52:10

페이즈 노이즈 발생시에 이를 최소화 할수 있는 방안이 있는지요?ADI12016.07.19

우선은 reference clock 및 VCO의 품질이 좋아야 합니다. 그 후 loop filter bandwidth , Icp등의 parameter설정을 통해 phase noise특성을 개선할 수 있습니다.진*일2016-07-19 오전 10:51:21

클럭출력에서, Main 클럭의 N 정수배 이외의 클럭주파수도 설정이 가능한가요?ADI12016.07.19

2nd PLL의 VCO출력의 정수배로 나누어진 값이 clock output 주파수가 됩니다.무명2016-07-19 오전 10:48:56

노이즈를 최소화 할수 있는 방안에는 어떤 방법들이 있는지 궁금 합니다,ADI12016.07.19

품질이 우수한 reference clock, vco 의 사용이 가장 중요합니다. 그 이후 회로 및 설정 값을 조절하는 것이 좋습니다.김*열2016-07-19 오전 10:47:09

모든 출력이 differential로 나가나요?ADI12016.07.19

HMC7044의 경우 CMOS를 지원합니다.진*일2016-07-19 오전 10:45:05

내부 VCO와 외부 VCO를 적용할 때, 클럭 Resolution과 지터성능은 어떠한 차이가 있나요?ADI12016.07.19

Close inband에서는 VCO의 특성을 따라 갑니다.이*기2016-07-19 오전 10:44:04

reference clock 의 페이즈 노이즈에 영향을 받나요?ADI12016.07.19

reference clock은 1st PLL의 narrowband loop filter에 의해 상당부분 noise가 제거되지만, reference clock의 영향이 있습니다.김*호2016-07-19 오전 10:43:54

아 출력은18개 output 이라고 내용에 나와있네요 ^^ADI12016.07.19

HMC7044의 경우 14개 입니다.김*호2016-07-19 오전 10:41:58

질문> HMC7044 의 경우 출력포트가 몇개까지 지원되나요?ADI12016.07.19

14개입니다.

EEWEBINAR

최신기사

Sponsored Links

[열린보도원칙] 당 매체는 독자와 취재원 등 뉴스이용자의 권리 보장을 위해 반론이나 정정보도, 추후보도를 요청할 수 있는 창구를 열어두고 있음을 알려드립니다.

고충처리인 강정규 070-4699-5321 , news@e4ds.com

[연재기획-사용후 배터리 산업②]2040년 폐배터리 폭발적 발생·EU 배터리법..

[연재기획-사용후 배터리 산업②]2040년 폐배터리 폭발적 발생·EU 배터리법..

AI 인프라發 고용량 메모리 채택↑, “하반기 공급 타이트”

AI 인프라發 고용량 메모리 채택↑, “하반기 공급 타이트”

델, “생성형 AI가 기업 성과 창출 도와”

델, “생성형 AI가 기업 성과 창출 도와”

.jpg) SKT, “통신사 전용 LLM 6월 출시”

SKT, “통신사 전용 LLM 6월 출시”

아이에스티이, HBM 이송용 풉 크리너 개발 하반기 납품

아이에스티이, HBM 이송용 풉 크리너 개발 하반기 납품

.jpg) 한국재료연구원 인사발령

한국재료연구원 인사발령

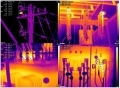

FLIR T5xx 열화상 카메라, 전기 점검 필수품 각광

FLIR T5xx 열화상 카메라, 전기 점검 필수품 각광

재료연 연구소기업 ㈜트윈위즈, 2024년 초기창업패키지 최종 선정

재료연 연구소기업 ㈜트윈위즈, 2024년 초기창업패키지 최종 선정

.jpg) KETI, 경남 기계·방산 기업 DX 솔루션 전주기 지원

KETI, 경남 기계·방산 기업 DX 솔루션 전주기 지원

기계연, 몽공 대기환경 개선 박차

기계연, 몽공 대기환경 개선 박차