연속시간 델타-시그마 ADC, AAF 설계 불필요

지터 완화 위해 개폐형 커패시터 DAC 등을

이용한 연구 등이 국내외에서 진행 중

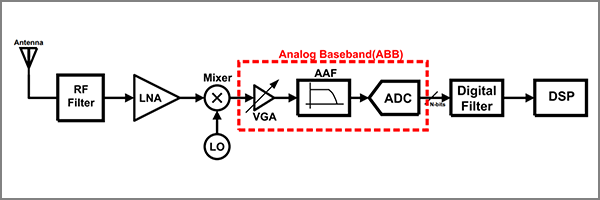

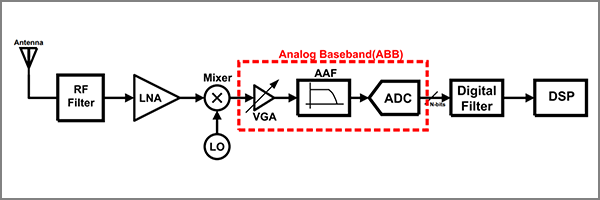

아날로그-디지털 변환기(Analog-to-digital converter; ADC)는 센서, IoT, 오디오, 통신시스템 등에서 필수적인 회로로, 최근 저전력의 고해상도 ADC 수요가 늘고 있다.

현재 통신시스템은 고속 아날로그 신호를 디지털로 변환하기 위해 플래시(Flash), 파이프라인(Pipeline), SAR ADC 등의 나이퀴스트(Nyquist) ADC 회로 구조를 주로 사용하고 있다.

근래 고속 회로에서 보다 높은 고해상도 성능을 요구하게 되면서 델타-시그마(delta-sigma; ΔΣ) ADC 구조를 이용하는 경우가 증가하고 있다.

이에 이승훈 서강대 전자공학과 교수는 지난 3일, 정보통신기획평가원(IITP)의 주간기술동향에 ‘20MHz 신호 대역에서 동작하는 고신뢰성 Continuous-Time Delta-Sigma ADC IP 기술’을 발표했다.

▲ 20MHz 신호 대역에서 동작하는 연속시간

델타-시그마 ADC IP 기술개념도 [그림=이승훈 교수]

연속시간(Continuous-time) 델타-시그마 ADC 구조가 저전력 측면에서 강점이 있으며, 이를 통해 DWA(Data-weighted averaging) 제거를 통한 칩 사이즈 감소와 제작 비용 절감이 가능하다고 이 교수는 설명했다. 연속시간 델타-시그마 ADC 구조는 위신호 제거 필터(Anti-aliasing filter; AAF) 효과가 회로 자체에 내재되어 별도의 관련 설계가 필요하지 않다.

이승훈 교수가 설계한 연속시간 델타-시그마 모듈레이터는 고속 무선통신 SoC와 고해상도 센서 애플리케이션에 적합하게 설계됐다. 20MHz 신호 대역까지 처리할 수 있으며, OSR(Oversampling ratio)을 16으로 정하여 640MHz 스위칭 주파수로 동작한다. 여기에는 3차 적분기와 4비트 양자화기가 사용되었고, 73dB의 SNR을 얻을 수 있다고 이 교수는 설명했다.

클럭 지터(Clock jitter)와 초과 루프 지연(Excess loop delay)에 취약한 연속시간 델타-시그마 모듈레이터의 단점을 보완하기 위해, 이 교수는 첫 번째 DAC는 NRZ(Non-return to zero) 방식을 사용하여 클럭 지터에 의한 영향을 줄였다. 두 번째 DAC와 세 번째 DAC는 디지털 미분기(Digital differentiator)로 구성하여 RZ(Return to zero) 펄스를 만듦으로써 초과 루프 지연을 보상했다고 설명했다.

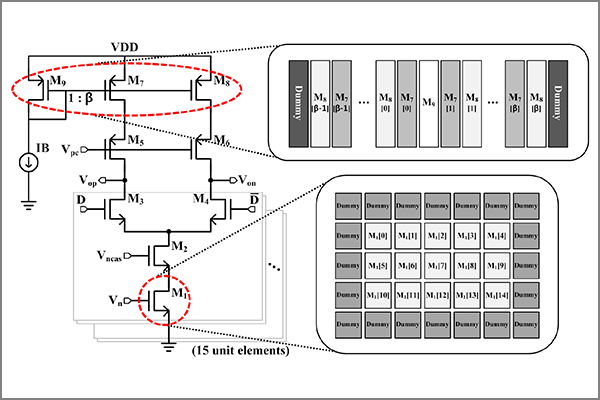

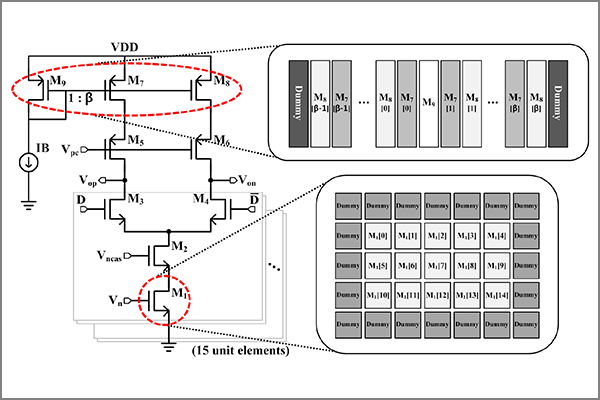

기존에는 DWA를 사용하여 미스매치 영향을 줄이는 방법을 사용하였으나 이 교수의 설계에서는 DAC 부분에 레이아웃 기술을 이용하여 미스매치 영향을 줄였다. 이 방법을 사용하면 DWA에서 사용되는 전력 소모를 줄일 수 있다.

▲ 전류 구동 DAC 회로 및 레이아웃 [그림=이승훈 교수]

이승훈 교수는 연속시간 델타-시그마 모듈레이터는 특성상 공정 변화율에 의한 계수 변화가 크므로 현재 손으로 계수를 트리밍하는 단계에서는 양산율이 95% 이상만큼은 되지 않으리라고 예상하면서도, 추후 자동으로 트리밍되는 로직을 설계하여 이 문제를 해결할 수 있다고 밝혔다.

◇ 지터 영향 완화 위해 개폐형 커패시터, 용량성 피드포워드 구조 등 국내외에서 연구 중

이 교수에 따르면 현재 국내에서는 연속시간 델타-시그마 ADC의 문제점 중 하나인 지터의 영향을 완화 시키기 위해 전류 구동(Current-steering) DAC 대신 개폐형 커패시터(Switched-capacitor) DAC를 이용한 연구가 진행 중이며, 이를 이용하면 지터로 인해 성능이 감소하는 문제를 PLL 없이 해결할 수 있을 것으로 예상했다.

또한, 전체 피드백(Full feedback) DAC 구조를 사용하면 각 DAC 회로가 증폭기(Amp) 출력단마다 붙어 증폭기의 속도를 높이기 위해서 많은 전력을 소모하는 단점이 있는데, 이를 해결하기 위해 용량성 피드포워드(Capacitive feedforward) 구조를 주로 사용하고 있다고 덧붙였다.

해외에선 △SNDR(Signal-to-noise and distortion ratio) 성능을 높이면서 안정성 문제를 완화하는 방법의 하나로 MASH(Multistage noise-shaping) 구조에 관한 연구가 활발하며, △VCO 양자화기 비선형성 제거(Quantizer nonlinearity cancellation) 기법을 사용하여 선형성 및 매칭 문제도 해결 중이며, △DNSQ(Double noise-shaped quantizer)라는 기법도 연구가 진행 중이라고 이 교수는 소개했다.

이승훈 교수는 최근 수십~수백 MHz 신호 대역에서 동작하는 연속시간 델타-시그마 ADC에 관한 논문들이 발표되고 있으며, FoM(Figure of merit) 측면에서도 발전되고 있다고 평가했다.