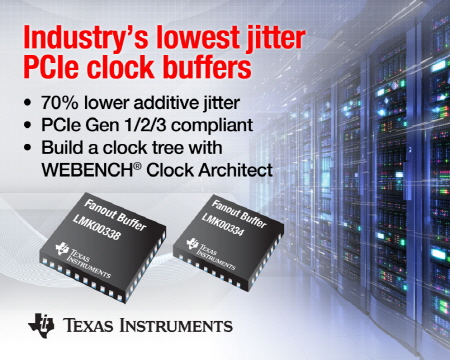

TI 코리아 (대표이사 켄트 전, Kent Chon, www.ti.com/ww/kr) 2014년 3월 14일 – TI(대표 이사 켄트 전)는 PCIe(PCI Express) 1.0, 2.0, 3.0 인터페이스를 지원하는 4출력 및 8출력 HCSL(high-speed current steering logic) 클럭 팬아웃 버퍼 2종을 출시했다. LMK00334는 입력 클럭에 대해 4개의 버퍼링한 사본을 생성하며, LMK00338은 8개의 버퍼링한 사본을 생성한다. 이들 디바이스는 가산 지터가 경쟁 디바이스 대비 70% 낮고, 훨씬 더 높은 공급 전원 잡음을 제거하여, 시스템 설계자에게 PCIe 3.0 규격에서 충분한 지터 마진을 제공한다.

두 디바이스는 모두 WEBENCH® 클럭 아키텍처에서 지원되며, 스위치, 라우터를 포함한 고속 통신, 네트워킹 및 데이터 센터 시스템을 위한 클럭 트리 설계를 간소화할 수 있도록 돕는다. (자세한 정보 및 샘플, 평가 모듈(EVM) 주문에 관한 내용은 http://www.ti.com/lmk00338-pr-kr 참조)

100MHz에서 30fs(PCIe 3.0), 1MHz ~ 20MHz에서 86fs(156.25MHz HCSL)로 전체 링크에 보다 유연한 타이밍 예산 할당 가능하며, 100MHz에서 -75dBc의 높은 PSRR(power supply rejection ratio)로 경쟁 디바이스보다 더 우수한 노이즈 내성과 지터 성능 제공한다. 또한 2개의 범용 입력이 최대 400MHz까지 동작하고, CML, LVPECL, LVDS, SSTL, HSTL, HCSL 또는 싱글엔디드(Single-Ended) 클럭 및 크리스탈 오실레이터를 포함한 모든 입력 유형과 호환 가능한 유연성을 가지고 있으며 핀 모드 제어로 시스템 설계자는 개별 출력 뱅크를 간편하게 켜고 끌 수 있다.

LMK00334 및 LMK00338은 CDCM9102 및 CDCM6208 같은 PCIe 클럭 제너레이터와 결합하여 고성능 클럭 트리 솔루션을 제공할 수 있다. TI의 클럭 분배기 및 팬아웃 버퍼는 클럭 트리 설계자에게 광범위한 통신, 네트워킹, 산업용 및 컨슈머 어플리케이션 구현에 필요한 유연성과 성능 및 향상된 기능을 제공한다.

엔지니어들은 TI의 WEBENCH® 클럭 아키텍트를 사용하여 LMK00334 및 LMK00338로 신속하게 클럭 트리 설계를 완료할 수 있다. 이 툴은 업계 최초의 타이밍 설계 툴로써, 광범위한 디바이스 데이터 베이스로부터 시스템 클럭 트리 솔루션을 권고하고 시뮬레이션할 수 있다. 여기에는 PLL(phase-locked loop) 필터 설계 및 출력 클럭의 위상 노이즈를 시뮬레이션할 수 있는 기능이 포함되어 있다. 또한, 완전한 클럭 트리를 위해 엔드-투-엔드(end-to-end) 지터 성능을 완전히 시뮬레이션하는 기능도 제공하고 있다.

LMK00334와 LMK00338은 모두 LMK00338 평가 모듈(EVM)을 사용하여 기능과 성능 규격을 검증할 수 있다. 시뮬레이션을 위한 LMK00334 및 LMK00338 IBIS 모델도 이용할 수 있다.

이 외에도 TI E2E™ 커뮤니티의 클럭 및 타이머 포럼에서 관련 솔루션을 검색할 수 있으며, 동료 엔지니어 및 TI 전문가와의 지식 공유 및 질의 응답 등으로 문제를 해결할 수 있다.