FPGA 상에서 최대 8k 해상도 및 HFR 영상

처리할 수 있도록 검증된 코드 자동 생성

매스웍스는 27일, 매트랩(MATLAB)과 시뮬링크(Simulink)의 릴리스 2019b에 포함된 비전 HDL 툴박스(Vision HDL Toolbox)를 통해 FPGA 상에서의 HFR(High Frame Rate) 및 고해상도 영상 처리를 위한 네이티브 다중 픽셀 스트리밍을 지원한다고 발표했다.

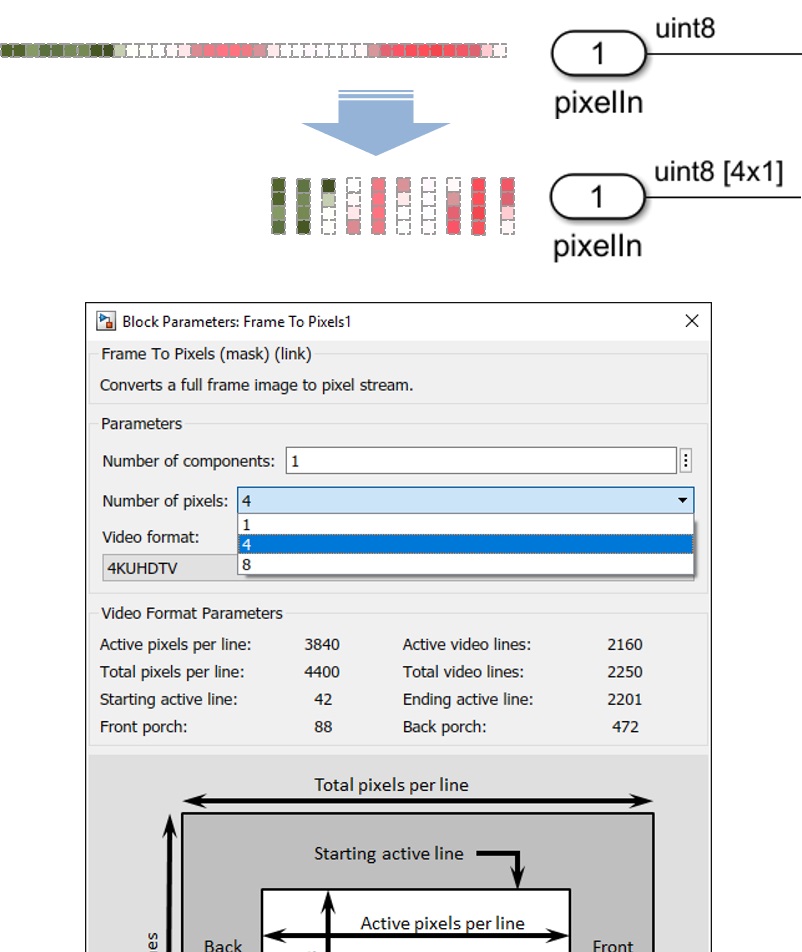

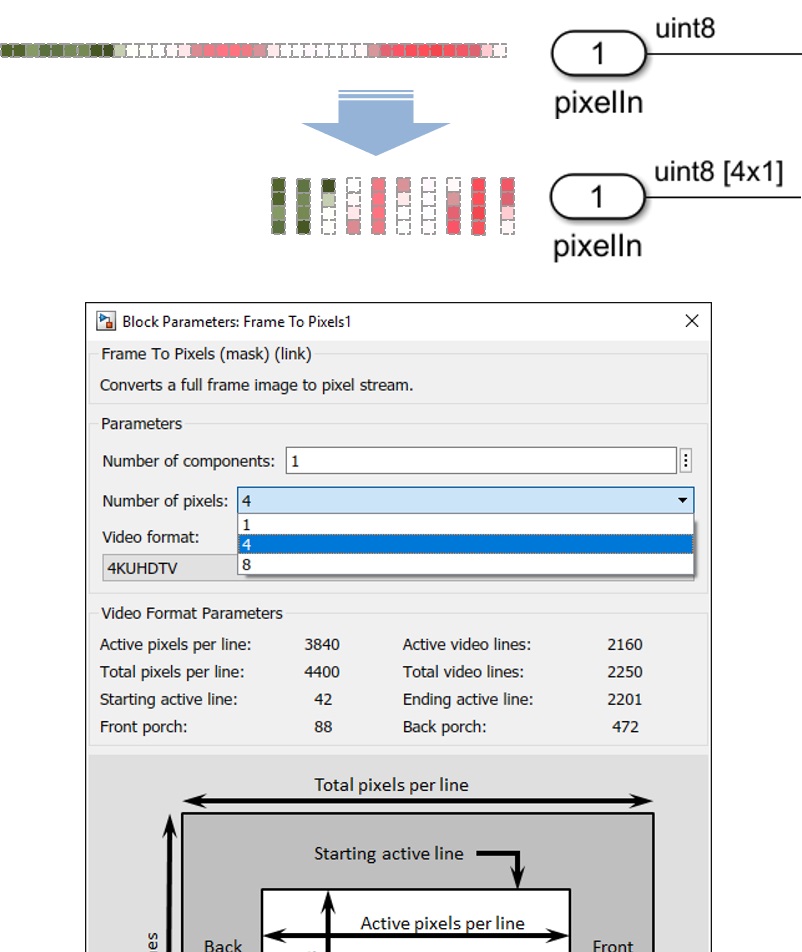

▲클록 당 1·4·8픽셀 처리를 빠르게 탐색하도록 지원하는 비전 HDL 툴박스 (이미지=매스웍스)

비전 HDL 툴박스는 영상, 이미지 처리 및 FPGA 설계 엔지니어가 4K나 8K 영상, 초당 240프레임 이상의 고해상도 영상 처리 시 시스템 동작 및 구현 간의 트레이드 오프를 탐색하거나 시뮬레이션하는 작업을 가속한다.

FPGA 설계 엔지니어는 산업용 검사, 의료 영상, 정보, 감시 및 정찰(ISR) 등의 애플리케이션에서 고해상도 및 HFR 영상의 실시간 처리를 구현하기 위해 처리량, 리소스 사용량 및 전력 소비량 목표를 충족시켜야 하는 도전과제에 직면해 있다.

비전 HDL 툴박스는 4나 8픽셀을 병렬 방식으로 처리하는 블록을 제공하며, 지정된 병렬 처리로 시뮬레이션 및 코드 생성을 수행하도록 기반 하드웨어 구현을 자동적으로 업데이트한다.

이러한 기능은 하드웨어 엔지니어가 이미지 및 영상 처리 엔지니어와 협업을 통해 높은 추상화 수준에서 비전 처리 하드웨어 동작을 탐색 및 시뮬레이션할 수 있도록 지원한다.

그뿐만 아니라 이러한 설계 워크플로우에 HDL 코더를 추가해 검증된 상위레벨 모델로부터 직접 결합 가능하며, 타깃 독립적이고, 최적화된 VHDL 또는 Verilog 코드를 생성할 수 있다.

비전 HDL 툴박스 R2019b는 지금 바로 사용할 수 있다.