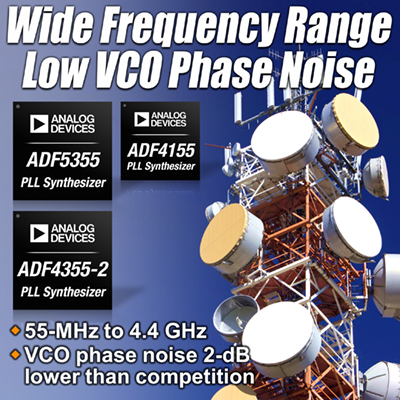

2014년 6월 12일 – 신호 처리 애플리케이션용 고성능 반도체 분야 글로벌 선도 기업인 아나로그디바이스(NASDAQ: ADI)는 업계 최대 주파수 범위와 최저 VCO(voltage-controlled oscillator) 위상 잡음을 단일 제품에서 구현 가능한 PLL(phase-locked loop) 제품 3종을 발표했다. 단일 고성능 광대역 합성기를 필요로 하는 RF 및 마이크로파 통신 시스템 설계자를 겨낭한 ADF5355 PLL은 동급 최대 대역폭인 55MHz~14GHz의 주파수 스펙트럼을 처리하며 ADF4355-2 PLL의 경우 55MHz~4.4GHz 주파수 범위를 처리한다. 두 제품 모두 초저 위상 잡음 VCO를 통합해 6GHz에서 1MHz 오프셋, -133dBc/Hz을 제공해 경쟁 제품보다 최소 2dB 감소한 잡음 성능을 자랑한다.

아나로그디바이스는 오늘 이 두 제품 외에도 독립형 8GHz 분수 분주형(fractional-N) PLL인 ADF4155도 함께 출시했다. 3가지 제품을 사용할 경우 설계자는 휴대전화 기지국, 마이크로파 P2P(point-to-point communication) 연결, 레이더 시스템, 평가 및 측정 기기 등 고사양의 초광대역 애플리케이션을 설계할 때 고주파수, 고전력 PLL과 VCO를 따로 사용하는 번거로움에서 벗어날 수 있다. 이번에 출시된 3종의 PLL은 PLL/합성기 설계자가 업계 최고 수준의 아나로그디바이스 PLL 솔루션 제품군을 사용해 최고의 성능을 구현할 수 있도록 무료 다운로드 소프트웨어인 ADIsimPLL™ 설계 툴이 최신 버전 3.6으로 지원된다. 신제품 PLL 합성기와 ADIsimPLL 툴은 6월 1~6일 사이 국제 마이크로파 심포지엄 장소에 위치한 아나로그디바이스의 415 번 부스에서 시연된 바 있다.

ADF5355와 ADF4355-2의 뛰어난 VCO 위상 잡음 성능은 아나로그디바이스의 특허 기술인 최신 SiGe 프로세서와 결합해 개발된 최신 VCO 토폴로지와 아키텍처를 통해 구현된다. 초광대역 RF 및 마이크로파 통신 애플리케이션에서 초저위상 잡음은 전체 시스템 오차율을 향상시키고 데이터 쓰루풋을 증가시켜 잡음 내성이 개선되고 대역폭 범위가 늘어나는 효과를 가져온다.

이외에도 아나로그디바이스의 비용 효율적인 신형 초광대역 PLL 합성기 IC는 최대 125MHz의 위상 비교회로 주파수 및 38비트 해상도를 제공해 지터를 낮추고 미세 단계폭을 허용한다. 최신 BiCMOS 공정을 통해 통합시키면 개별로 GaA를 사용하는 것과 비교해 패키지 크기와 전력 소모를 크게 감소시킬 수 있다. 또한, 단일 PLL이 55MHz~14GHz 사이의 주파수에서 작동하도록 구성 가능해 다중 주파수 대역을 지원하면서도 설계자가 더욱 빠르게 시스템 설계를 재구성하고 부품 재고를 줄일 수 있다.

신형 PLL 3종은 AD9361 RF 고속 트랜시버™용 오실레이터와 AD9625 12비트, 2GSPS A/D 컨버터용 클럭으로 사용되는 ADL5801 능동 믹서, ADL5375 광대역 쿼드러처 모듈레이터, ADL5380 광대역 쿼드러처 IQ 디모듈레이터 등 ADI의 기타 RF 부품을 사용한 설계에도 적합하다.