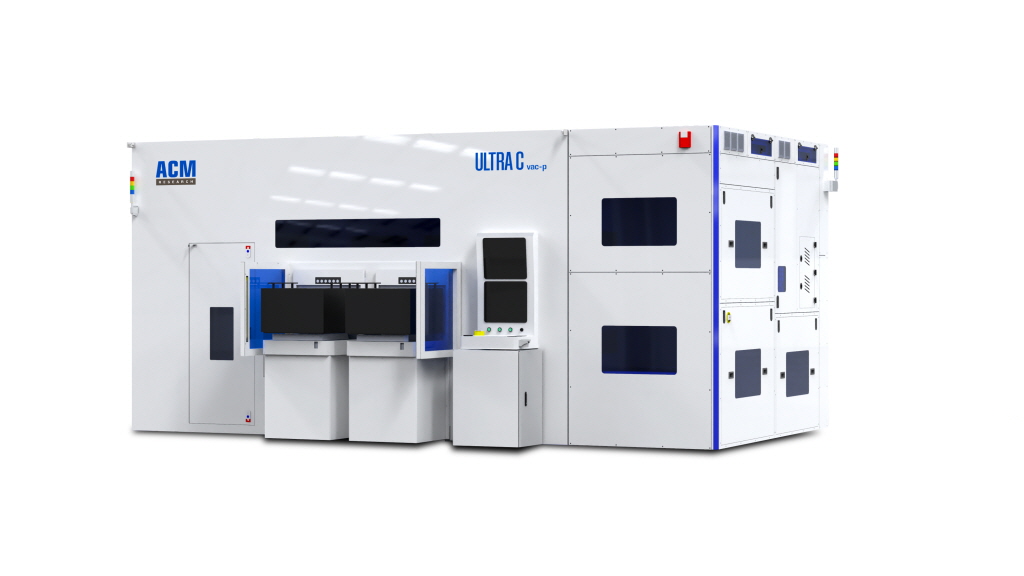

Ultra C vac-p 패널 레벨 첨단 패키징 진공 세정 장비 출시

반도체 및 첨단 웨이퍼 레벨 패키징(WLP) 애플리케이션을 위한 웨이퍼 처리 솔루션 전문 기업인 ACM 리서치(ACM Research, Inc.)가 진공 기술과 IPA 건조 기술을 활용해 세정 효율을 높여 경제적이고 효율적인 반도체 첨단 패키징을 구현했다.

ACM은 팬아웃형 패널 레벨 패키징(FOPLP) 애플리케이션에 적합한 Ultra C vac-p 진공 세정 장비를 출시했다고 7일 밝혔다.

이 장비는 진공 기술을 이용해 칩렛 구조 내의 플럭스 잔여물을 제거하며, 세정 효율을 크게 향상시켰다.

이는 ACM이 고성장 중인 팬아웃형 패널 레벨 패키징 시장에 성공적으로 진입했음을 의미한다.

ACM은 한 중국 대형 반도체 제조회사가 Ultra C vac-p 패널 레벨 진공 세정 장비를 주문했으며, 해당 장비는 7월에 이 고객의 공장에 납품됐다고 발표했다.

ACM의 사장겸 CEO인 데이비드 왕(David Wang) 박사는 “인공지능(AI), 데이터센터 및 자율 주행 자동차 시장을 중심으로 더욱 강력한 연산 능력과 더 낮은 지연 시간, 그리고 더 높은 대역폭이 요구됨에 따라 FOPLP는 이제 핵심적인 기술로 떠오르고 있다”며 “FOPLP는 여러 칩, 수동 소자 및 인터커넥트를 패널 상의 단일 패키지에 통합하여 더 높은 유연성, 확장성 및 비용 효율성을 제공한다. Ultra C vac-p 패널 레벨 진공 세정 장비는 ACM이 차세대 첨단 패키징 기술의 세정 문제를 해결하는 데 중요한 걸음을 내디뎠음을 나타내며, 반도체 제조 분야의 지속적인 혁신을 상징한다. 이는 ACM이 지속적으로 변화하는 업계 요구를 충족시키기 위해 노력하고 있다는 확고한 약속을 실현한 것”이라고 말했다.

욜 그룹(Yole Group)에 따르면, 팬아웃형 패널 레벨 패키징 방법의 애플리케이션 성장 속도는 팬아웃 시장 전체 성장 속도보다 빠르며, 시장 점유율은 2022년 2%에서 2028년 8%로 증가할 것으로 예상된다.

FOPLP 성장의 주요 동력은 비용 절감이다. 예컨대 전통적인 실리콘 웨이퍼는 형태가 원형이라 웨이퍼의 사용률이 85% 미만인 반면, 패널은 형태가 직사각형 또는 정사각형 이기 때문에 웨이퍼 사용률이 95% 이상이다.

600 x 600㎜ 패널의 유효 면적은 기존 300㎜ 실리콘 웨이퍼 유효 면적의 5.7배로, 전반적으로 약 66%의 비용 절감이 가능하다. 이러한 면적 활용률의 증가는 더 높은 생산성, 더 큰 AI 칩 설계 유연성 및 상당한 비용 절감을 가져온다.

Ultra C vac-p 장비는 첨단 패키징 공정의 중요한 단계를 처리하며, 특히 언더필 전에 플럭스 잔여물을 제거하는데, 이는 보이드(void), 즉 언더필 간극을 없애는 데 있어서 중요한 작업이다.

기존의 세정 방법은 표면 장력과 제한된 액체 침투력 때문에 작은 범프 간격(40 마이크로미터 이하)과 대형 칩을 처리하는 데 있어서 어려움을 겪는다.

ACM의 새로운 장비는 진공 세정을 통해 세정액이 좁은 틈에 도달할 수 있도록 하여 이 문제를 효과적으로 해결한다.

또한 세정액이 더 긴 거리를 통과해야 하기 때문에 기존 방법으로는 처리할 수 없던 대형 칩 유닛의 세정 요구도 충족할 수 있다.

이 진공 세정 기능 장비는 ACM 고유의 IPA 건조 기술을 결합함으로써 전체 칩 유닛, 심지어 중심 부분까지도 철저히 세정할 수 있어 잔여물이 장치 성능에 미치는 영향을 효과적으로 방지할 수 있다.

Ultra C vac-p 패널 레벨 진공 세정 장비는 유기 재료 또는 유리 재료로 만들어진 패널에 맞게 설계되었다.

이 장비는 510 x 515㎜ 및 600 x 600㎜ 패널과 최대 7㎜까지의 패널 휨을 처리할 수 있다.