통합 이더넷 및 인터라켄, 암호화 엔진 지원

현세대 FPGA보다 처리량 최대 3배 높아

PCIe Gen5 및 내장 DMA, CCIX, CXL 제공

열적 혹은 공간적 제약이 있는 환경에서 동작하는 고대역폭 네트워크 및 확장과 적응할 수 있는 애플리케이션 가속화가 필요한 클라우드 서비스 업체들을 위해 설계된 적응형 컴퓨팅 가속화 플랫폼(Adaptive compute acceleration platform; ACAP)이 공개됐다.

자일링스는 11일, 버설(Versal) ACAP 제품군의 세 번째 시리즈인 ‘버설 프리미엄(Versal™ Premium)’을 발표했다. 버설 프리미엄은 적응형 플랫폼상에 상호 연결된 전력 최적화된 코어를 통합하고 있으며, 높은 대역폭과 컴퓨팅 밀도를 제공한다.

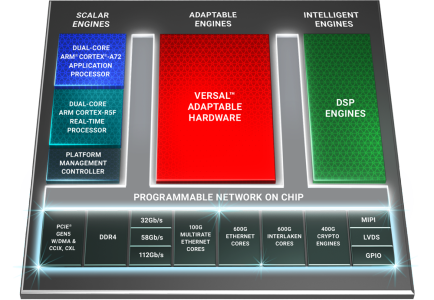

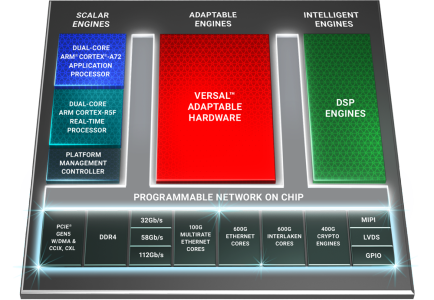

▲7nm 공정에서 제작된 버설 프리미엄 (출처=자일링스)

TSMC의 7nm 공정 기술로 개발된 버설 프리미엄은 소프트웨어 프로그래밍 기능과 동적으로 구성 가능한 하드웨어 가속화 기능을 비롯해 사전 설계된 연결 및 보안 기능을 모두 갖추고 있어 시장 출시시간을 단축할 수 있다.

빠르고 안전한 네트워크를 구현할 수 있도록 통합 이더넷 및 인터라켄(Interlaken), 암호화 엔진을 지원함으로써 현세대 FPGA보다 최대 3배 높은 처리량을 제공한다.

따라서 현재 구축된 주요 FPGA의 컴퓨팅 밀도를 2배로 높이는 것은 물론, 점점 진화하는 클라우드 및 네트워킹의 작업부하에 대응할 수 있는 적응형 기능을 제공한다.

버설 프리미엄은 현재 공급 중인 버설 AI 코어 및 버설 프라임(Versal Prime) ACAP 시리즈를 기반으로 구현됐다. 112Gbps PAM4 트랜시버와 수백 기가비트의 이더넷 및 인터라켄 연결, 고속 암호화 및 PCIe® Gen5를 비롯해 내장 DMA와 CCIX 및 CXL을 지원한다.

또한, 바이티스(Vitis™) 통합 소프트웨어 플랫폼 및 비바도(Vivado®) 디자인 수트와 함께 하드웨어 및 소프트웨어 개발자를 위한 솔루션 스택을 제공하여 생산성을 높인다.

네트워크 속도 및 안전 향상

5G 네트워크의 등장으로 네트워크 트래픽이 증가하면서 기존 설치공간 및 전력규격 내에서 전력 최적화된 처리량 및 컴퓨팅 밀도에 대한 요구가 높아지고 있다.

버설 프리미엄 시리즈는 최대 9Tb/s까지 확장 가능한 적응형 직렬 대역폭을 제공함으로써 이러한 문제를 해결한다. 112G PAM4 트랜시버와 통합 연결 기능을 활용하여 코어, 메트로, DCI(Data center interconnect) 인프라에서 포트당 대역폭 밀도를 2배로 늘리고, 지연시간을 최대 50%까지 줄일 수 있다.

사전 설계된 연결 기능은 다양한 데이터 속도 및 프로토콜을 지원할 수 있는 유연성을 갖추고 있어 수 테라비트의 이더넷을 구현할 수 있다.

채널화된 이더넷 코어는 설치공간을 최소화하면서도 최대 5Tb/s의 처리량을 제공하며, 고속 암호화 엔진은 최대 1.6Tb/s의 암호화된 라인 속도 처리량과 AES-GCM-256/128, MACsec, IPsec 등을 지원한다.

적응형 클라우드 가속

버설 프리미엄은 하이퍼스케일 컴퓨팅의 광범위한 데이터센터 작업부하에 대해 최고 수준의 가속화를 달성할 수 있도록 설계되었다.

사용자 지정이 가능한 데이터 계층구조와 120TB/s 이상의 온칩 데이터 대역폭을 통해 주요 병목현상을 제거하고, 데이터 이동을 줄일 수 있으며, 사전 설계된 연결 기능과 코어를 통해 기존 클라우드 인프라에 드롭인(Drop-in) 통합이 가능하다.

버설 프리미엄 시리즈는 2021년 상반기에 조기사용 고객을 대상으로 샘플이 공급될 예정이다. 현재 문서자료가 제공되고 있으며, 고객들은 버설 프라임 평가 키트를 통해 시제품 제작을 시작할 수 있다. 버설 프라임 디바이스는 버설 프리미엄 디바이스와 같은 아키텍처 블록으로 구현되어 있으며, 버설 프리미엄으로의 핀 마이그레이션이 지원된다.