MCU, 미세가공 고속 회로 제작 최적

ST, 다른 대륙 제품 생산 자연재해 공급 안정성 확보

미세가공 장단점 보완, 낮은 대기전류·노이즈에 강해

[편집자주]일반적으로 반도체라 하면 컴퓨터의 CPU와 메모리처럼 일반인에게 익숙한 반도체를 떠올리기 마련이다. 반면에 전자제품 구동을 위해서 핵심 반도체로 쓰이는 MCU(Micro Controller Unit)의 경우 일반적으로 우리가 쉽게 접하는 모든 전자제품에서 사용되고 있으면서도 일반인에게는 아직 낯선 반도체다. 이런 MCU가 최근 반도체 부족 사태로 인해 언론에 오르내리며, 일반인들에게 주목받기 시작했다. 이에 본지는 MCU 반도체 전문기업인 ST마이크로일렉트로닉스의 유지 카와노 매니저의 연재기고를 통해 MCU에 대해 전문적으로 알아보는 자리를 마련했다.

■ 실리콘 웨이퍼 상의 MOS 제조 중요

■ 실리콘 웨이퍼 상의 MOS 제조 중요

MCU 생산 공정에는 몇 개의 단계가 있다. 각각의 MCU는 수많은 MOS 트랜지스터로 구성되어 있다. MOS 트랜지스터를 보다 정확하게는 MOSFETs(metal oxide semiconductor field effect transistors)이라고 하며, 이 글에서는 간단히 MOS로 쓴다. MOS 생산 공정의 중요한 부분은 실리콘(원소 기호: Si) 웨이퍼 상의 MOS의 제조(fabrication)이다. 이 글에서는 MCU 생산과 관련된 다양한 공정을 살펴 볼 것이다. 이러한 공정 지식은 MCU를 쓰는 엔지니어들에게 반드시 필요하다.

■ 업스트림 및 다운스트림 공정

MCU 생산 공정은 크게 두 부분으로 나눌 수 있다. 첫 번째 공정은 실리콘 웨이퍼 디스크 상에 MOS를 구현한 다음 로직 및 아날로그 회로를 만들기 위해 금속 스트립으로 MOS들을 배선한다. 두 번째 공정은 MCU 칩 단위로 실리콘 웨이퍼를 절단한 다음 일반적인 IC 형태를 만들어내고 각각의 칩을 패키지에 하우징한다. 첫 번째 공정을 업스트림 공정이라고 하며, 두 번째 공정을 다운스트림 공정이라고 한다. 업스트림 공정은 웨이퍼 공정 또는 웨이퍼 가공이라고도 하며, 다운스트림 공정은 어셈블리라고도 한다. 그림 1은 이러한 공정을 다이어그램으로 나타낸 것이다. 위쪽이 업스트림 공정이며, 아래쪽이 다운스트림 공정이다.

지금은 MCU 고객들이 MCU 제조 공장에 대해서도 주의를 기울이는 데, 최근 대규모 재난(예를 들어, 지진)으로 인해 주요 MCU 제조업체들의 업스트림 및 다운스트림 공장에 피해가 발생하여 제품 공급 과정에 문제가 발생했기 때문이다.

ST마이크로일렉트로닉스(이하 ST)는 이와 같은 주요 자연재해로부터의 공급 안정성을 확보하기 위해 다른 대륙에 있는 두 개 이상의 공장에서 제품을 생산한다는 원칙을 갖추고 있다. 두 개 이상의 공장에 업스트림 공정을 할당하고, 다른 두 개 이상의 공장에 다운스트림 공정을 할당한다. 이러한 체제는 주요 자연재해로 인해 공장 중 하나가 피해를 입을지라도 ST의 MCU 공급 중단을 방지하기 위함이다.

▲그림 1: 업스트림 및 다운스트림 공정

▲그림 1: 업스트림 및 다운스트림 공정

MCU 공정 명칭에서 길이는 무엇을 의미하는가?

MCU 카탈로그, 매뉴얼 또는 신제품 기사 등에서 ‘180㎚ CMOS 공정’ 또는 ‘90㎚ 공정’ 등과 같은 표현을 볼 수 있다. 또한 ‘미세가공 공정’ 또는 ‘공정 미세화’ 등에 대해서도 들어 보았을 것이다. 이러한 용어들의 의미는 무엇인가?

반도체에 대해 어느 정도 지식이 있다면, 180㎚, 90㎚ 등과 같은 감소하는 숫자들이 소형화를 의미하고 숫자가 작아질수록 공정이 보다 개선되었다는 것을 알 수 있을 것이다. 하지만, MCU에서 이러한 숫자들이 의미하는 바는 무엇일까?

이러한 숫자들은 미세가공 웨이퍼 영역의 최단(최소) 부분의 크기를 나타낸다. 이것은 ‘공정의 최소 외형 크기(minimum feature size)’를 의미한다. 그러나 보다 구체적으로 어떤 부분의 최단 거리인가?

각기 다른 MCU 제조업체들은 각기 다른 최소 외형 크기의 공정을 사용하고 있다. 예를 들어, 금속 배선막 폭이 가장 짧다면 그 폭이 최소 외형 크기이며, 반면 MOS 게이트 길이가 가장 짧다면 그 길이가 최소 외형 크기이다. 대부분의 경우, MOS 게이트 길이가 최소 외형 크기이다.

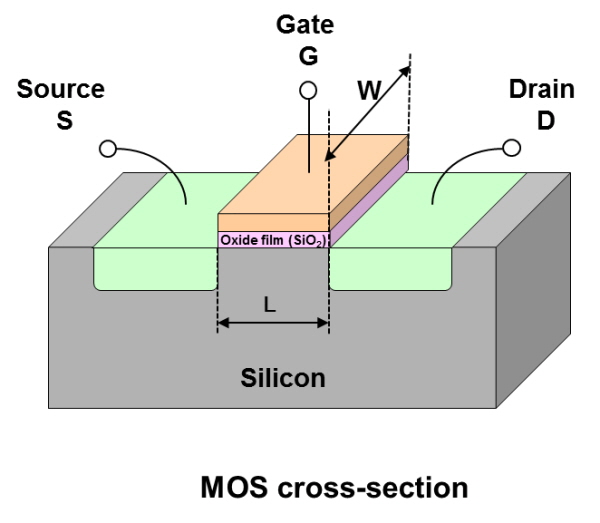

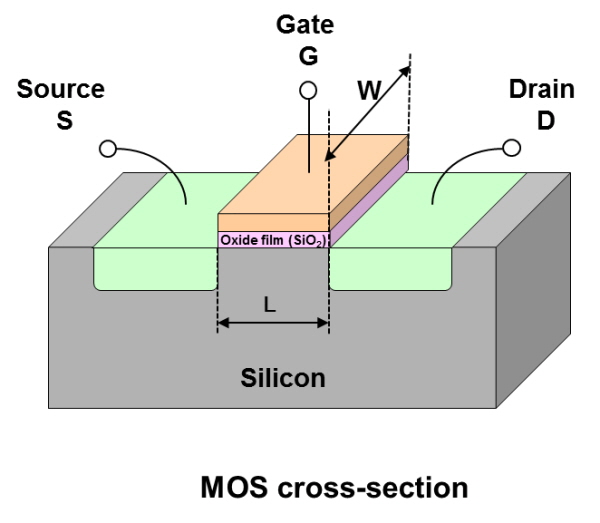

▲그림 2 : MOS의 단면도

그림 2는 MOS의 단면도이다. 드레인과 소스 사이의 길이가 게이트 길이(L)이다. 게이트의 다른 면의 크기가 게이트 폭(W)이다.

게이트 길이는 MOS 스위칭 속도, 드레인과 소스 사이를 통과하는 전류, 게이트 커패시턴스 등에 영향을 미친다. 이러한 이유로 인해 L 값이 공정 명칭에 일반적으로 사용된다.

180㎚ CMOS 공정은 180㎚의 MOS 게이트 길이를 갖는다. MOS 게이트는 CMOS 구조에서 최단 길이를 갖는다. MOS 크기가 작아지는 것((L = 90 ㎚ 등과 같이)을 공정 미세화(process shrink)라고 한다.

ST의 MCU의 경우, STM32F103 시리즈는 180㎚ CMOS 공정에서 생산되며, STM32F429 시리즈는 90㎚ CMOS 공정에서 생산된다.

CMOS는 무엇인가?

.jpg)

▲그림 3: 다양한 MOS 회로

MCU 공정 명칭에서, 최소 외형 크기 다음에 ‘상보성(complementary) MOS’의 약자인 CMOS가 이어진다. CMOS는 p-채널 MOSFETs과 n-채널 MOSFETs이 상보적 배열로 구성된 게이트 구조를 갖는 트랜지스터이다. p-채널 MOS(PMOS라고도 함)는 게이트에 전압이 인가되면 OFF 상태로 전환되고, n-채널 MOS(㎚OS라고도 함)는 게이트에 전압이 인가되면 ON 상태로 전환된다. 그림 3은 CMOS, ㎚OS, PMOS 회로로 구성된 인버터 회로(논리 NOT 연산자)를 나타낸 것이다.

㎚OS 및 PMOS 회로는 상대적으로 많은 양의 에너지를 소비하는 데, MOS가 ON 상태로 전환되면 직접 전류가 레지스터와 MOS를 통과하기 때문이다. 그러나, MOS 중 하나는(이론적으로) 항상 OFF 상태로 설정되어 있기 때문에 직접 전류가 CMOS 회로를 통과하지 않으므로 이 회로는 낮은 전력소모 특성을 갖는다. 현재 거의 모든 MCU가 CMOS 구조로 되어 있다.

■ 공정 미세화가 전체 비용 낮춰

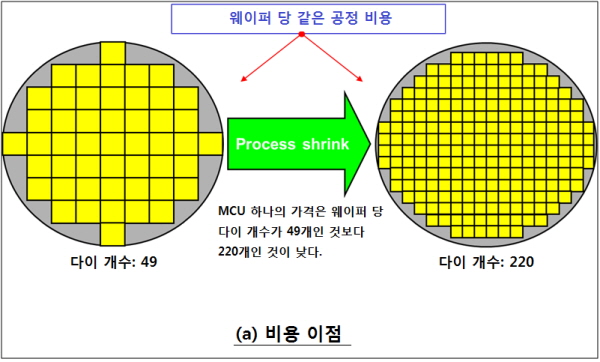

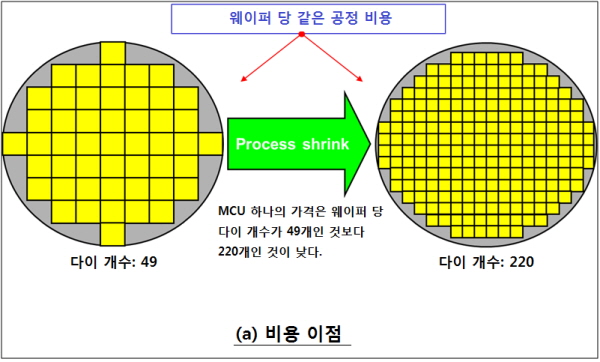

▲그림 4(a) : 공정 미세화의 이점 (1/2)

MCU 생산 라인 상에서 각 웨이퍼는 일괄-처리(sheet-process)되기 때문에 웨이퍼 상의 MCU 개수와 무관하게 웨이퍼 당 비용은 동일하다. 따라서, 웨이퍼 상에서 가능한 한 많은 수의 MCU를 제조할수록 비용을 절감할 수 있다. 그림 4(a)는 이를 설명하는 다이어그램이다. 하지만, 실제로 이러한 간단한 계산방법을 통해서 비용을 결정할 수는 없다. 공정 미세화는 포토-마스크와 생산 라인의 비용을 증가시킨다. 또한 리드와 다이(칩)을 연결하는 본딩 패드는 일정한 기계적 크기를 갖기 때문에 다이(칩) 크기를 MOS 크기와 함께 무한정 줄일 수 없다. 그러나 다이어그램을 통해 일반적으로 말하자면 공정 미세화가 전체 비용을 낮추는 경향이 있다는 것을 확인할 수 있다.

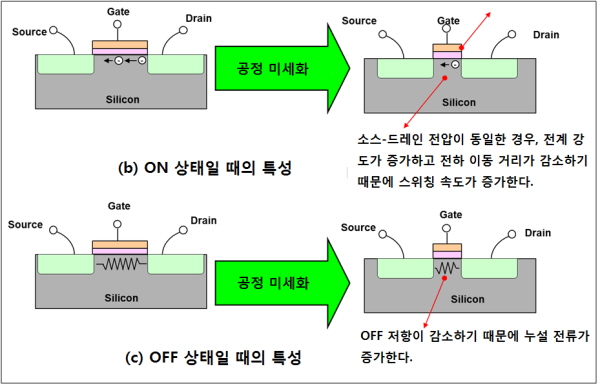

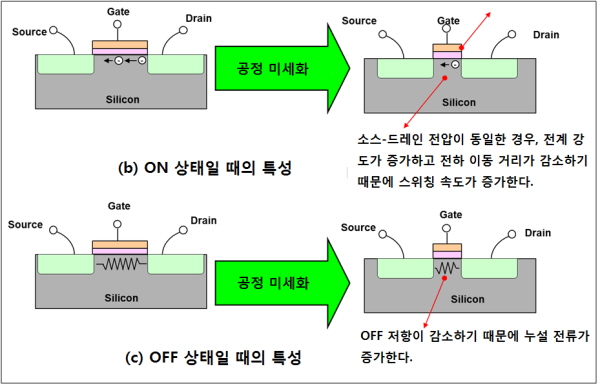

▲그림 4(b),(c) : 공정 미세화의 이점 (2/2)

그림 4(b)에 나타낸 바와 같이 미세가공(microfabrication)을 통해 MOS 스위칭 속도를 증가시킴으로써 결과적으로 고속 회로를 제작할 수 있다. 하지만 그림 4(c)에 나타낸 바와 같이 회로가 OFF 상태일 때 상대적으로 큰 누설 전류가 발생하기 때문에 MCU 대기 전류가 증가하게 된다. 또한 미세 회로들은 외부 신호에 쉽게 영향을 받을 수 있기 때문에 결과적으로 노이즈에 취약하다.

이것은 공정 미세화가 장점과 단점을 모두 가지고 있다는 것을 의미한다. 그러나 단점을 보완하고 장점을 극대화하고 있는 개발 엔지니어들 덕분에 오늘날 미세가공 MCU는 낮은 대기 전류와 노이즈에 강한 특성을 가지고 있다.

■ 실리콘 웨이퍼 상의 MOS 제조 중요

■ 실리콘 웨이퍼 상의 MOS 제조 중요

.jpg)