인텔 FPGA 디자인 소프트웨어 Quartus가 알려주는 디버깅 팁

FPGA 디자인을 하다보면 작성된 프로그램이 정확한지, 잘못은 없는지 확인하는 디버깅 작업을 거쳐야 한다.

그렇다면 어떻게 해야 디버깅 작업을 좀더 쉽고 빠르게 할 수 있을까. FPGA의 오류를 수정하기 위한 디버깅 툴인 인텔의 FPGA 디자인 소프트웨어는 이 물음에 만족할 만한 답을 해준다.

이 ‘Quartus’에는 ▶SignalProbe Incremental Routing ▶In-System Memory Content Editor ▶In-System Sources & Probes ▶SignalTap II embedded logic analyzer ▶Logic Analyzer Interface까지 다섯개의 디버그 툴이 포함되어 있다.

먼저, SignalProbe Incremental Routing은 특정 로직셀을 전체 컴파일하지 않아도 외부 핀으로 연결하여 로직 분석기나 오실로스코프 등으로 확인할 수 있도록 도와준다. 일반적으로 FPGA의 경우 내부 시그널을 외부로 연결하기 위해서는 내부의 리소스를 사용하기 때문에 Fitting과 Routing 작업을 같이해야 한다. 그러나 Incremental Routing 기능은 기존에 사용하지 않는 루팅 리소스를 이용하여 외부로 연결하기 때문에 빠른 작업을 할 수 있다. .

또한 ‘In-System Memory Content Editor’는 JTAG(Joint Test Action Group)를 통해서 내부 메모리의 내용을 확인하고 업데이트하기 위해 사용한다. ISMCE는 디바이스 동작 중에도 내부 메모리를 수정하거나 업데이트할 수 있는데 JTAG 컨트롤러를 통해서 일어나기 때문에 연결되어 있어야 한다. ISMCE가 지원하는 IP는 LPM_CONSTANT, 싱글 포트 ROM과 RAM이 있다.

‘In-System Sources & Probes’도 마찬가지로 JTAG를 통해 동작한다. 각각의 ISSP에는 런타임동안 최대 512개까지 프로브와 토글이 가능하다. 간단한 Function 디버깅에서 ISSP IP의 Instance가 가능한 경우는 JTAG를 디버깅 채널로 이용하기 때문에 연결이 반드시 필요하며 추가적인 외부장치 없이 PC환경에서 사용할 수 있다.

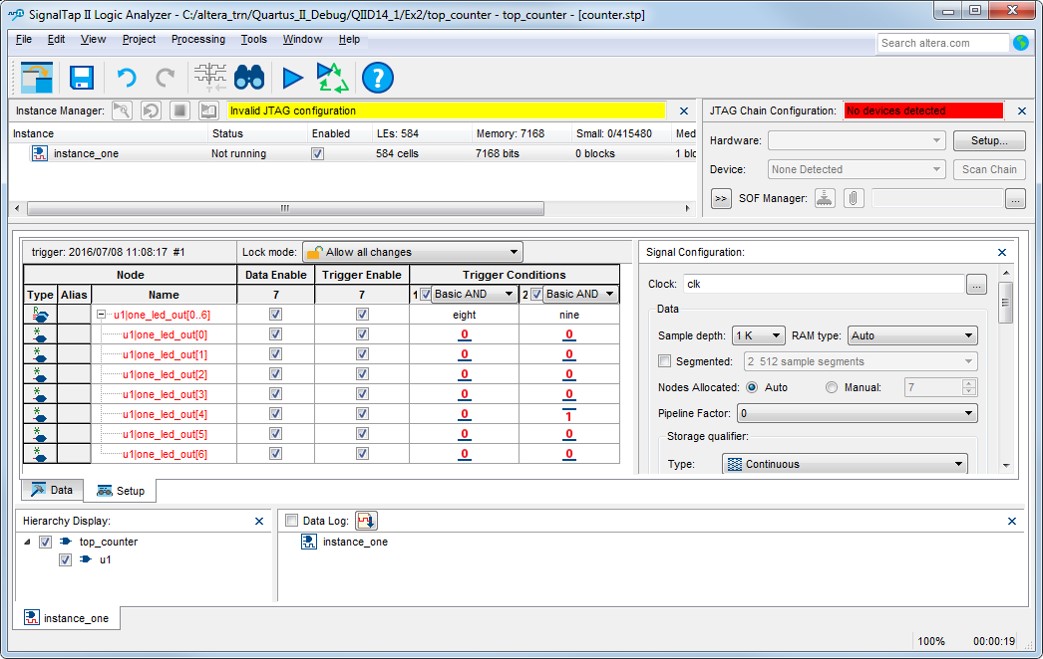

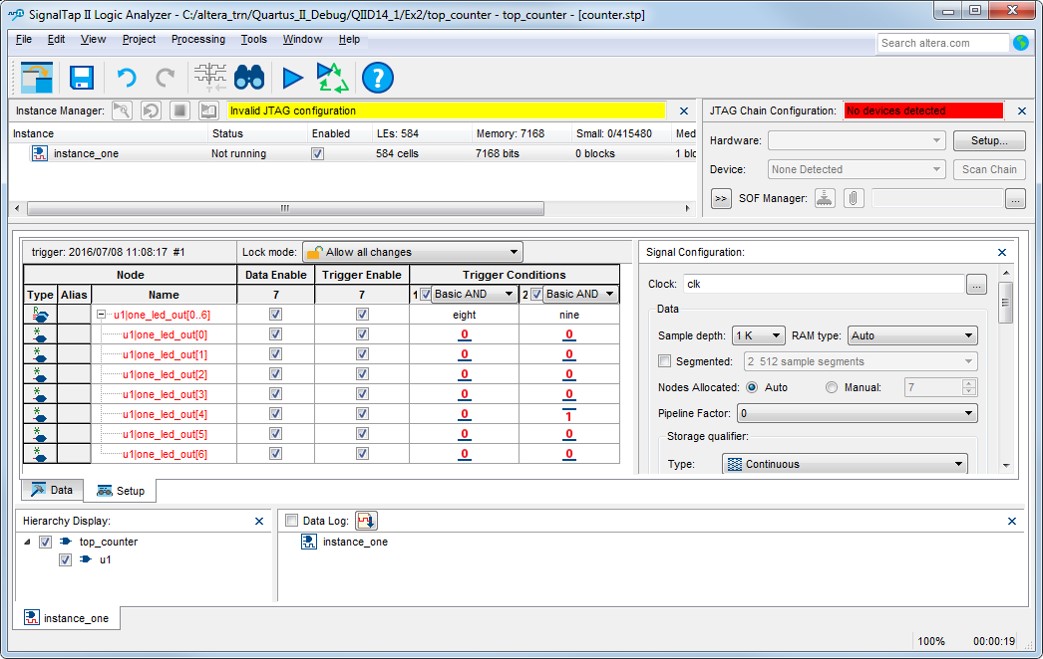

‘SignalTap II embedded logic analyzer’의 기능은 미리 정의된 클럭 시그널을 이용해서 내부의 신호를 모니터링 하는 것이다. 실시간으로 다양한 신호를 모니터링할 수 있다. 완성한 custom code에 SignalTap II을 추가하고 목표하는 프로브 포인트를 선택하여 트리거 조건을 잡아 준다. 다음 전체 컴파일하고 결과값을 디바이스에 프로그래밍한다. 분석결과는 SignalTap II의 디버깅 GUI를 통해 볼 수 있다.

마지막으로 FPGA 내부의 신호들을 가시성을 높이기 위해 사용하는 것이 ‘Logic Analyzer interface’이다. 내부 신호들을 I/O 핀과 연결한 후 외부 테스트 자아비와 연결해 주는 것이다. 최대 256개의 내부 신호를 각 핀들과 연결할 수 있으면 내부 프로브 포인트를 빠르게 스위칭해 연결할 수도 있다. 작업을 위해 따로 다시 컴파일하거나 재구성할 필요 없다.

인텔의 Axios FAE 전현수 차장은 "인텔 ‘Quartus’는 사용자가 접근이 편하도록 GUI 환경이 직관적으로 되어 있다. 디버깅 툴 또한 기본적인 internal logic에 대한 디버깅을 포함해서, 트랜시버 등 특화된 블록까지도 디버깅이 가능하다"며 "디버깅 툴을 사용할 때 JTAG의 연결만 확보한 후 상황에 따른 적절한 툴을 사용하는 것이 중요하다"고 말했다.

인텔 Quartus 디버깅 툴에 대한 자세한 설명과 각각의 디버그 상황에 맞춰 적절하게 대처할 수 있는 디버깅 툴의 활용법은 온라인 웨비나(eeWebinar)에서 다시 볼 수 있다.